# Midterm Exam

(February 17<sup>th</sup> @ 7:30 pm)

Presentation and clarity are very important! Show your procedure!

# **PROBLEM 1 (20 PTS)**

• Compute the result of the following operations. The operands are signed fixed-point numbers. The result must be a signed fixed point number. For the division, use x = 5 fractional bits.

| 1.010001 + | 1001.1101 - | 0.010101 + |

|------------|-------------|------------|

| 1.011      | 1.011101    | 01.11111   |

| 10.101 ×   | 1.011 ×     | 10.10010 ÷ |

| 0.10011    | 1.0101      | 0.101      |

# **PROBLEM 2 (10 PTS)**

Represent these numbers in Fixed Point Arithmetic (signed numbers). Use the FX format [12 4].

✓ -16.375

✓ 32.3125

• Complete the table for the following fixed point formats (signed numbers): (6 pts.)

| Integer bits | Fractional Bits | FX Format | Range | Resolution |

|--------------|-----------------|-----------|-------|------------|

| 6            | 3               |           |       |            |

| 8            | 5               |           |       |            |

# PROBLEM 3 (40 PTS)

Perform the following 32-bit floating point operations. For fixed-point division, use 4 fractional bits. Truncate the result when required. Show your work: how you got the significand and the biased exponent bits of the result. Provide the 32-bit result.

✓ C1500000 + 436A0000 ✓ D0A90000 - CF480000 ✓ 80400000 × 7AB80000 ✓ FBB80000 ÷ 49400000

### PROBLEM 4 (30 PTS)

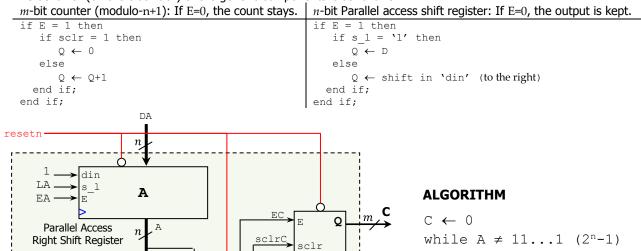

- "Counting 0's" Circuit: It counts the number of bits in register A with a '0' value. The digital system is depicted below.

- ✓ Example: for n = 8: if A = 00110010, then C = 0101.

LA EA

s clock

✓ The behavior (on the clock tick) of the generic components is as follows:

**FINITE STATE**

MACHINE

counter: m bits

$m = \lceil \log_2(n+1) \rceil$

DATAPATH CIRCUIT

done

1

# $C \leftarrow 0$ while A ≠ 11...1 (2<sup>n</sup>-1) if $a_0 = 0$ then $C \leftarrow C + 1$ end if right shift A end while

- Sketch the Finite State Machine diagram (in ASM form) given the algorithm (for n=8, m=4). (18 pts.)

- ✓ The process begins when s is asserted, at this moment we capture DA on register A. Then, we shift A one bit at a time. The process ends when  $A = 2^n 1$  (i.e., when z=1). The signal done is asserted when we finish counting.

- ✓ As *A* is being shifted: we need to increase the count C every time  $a_0 = 0$ .

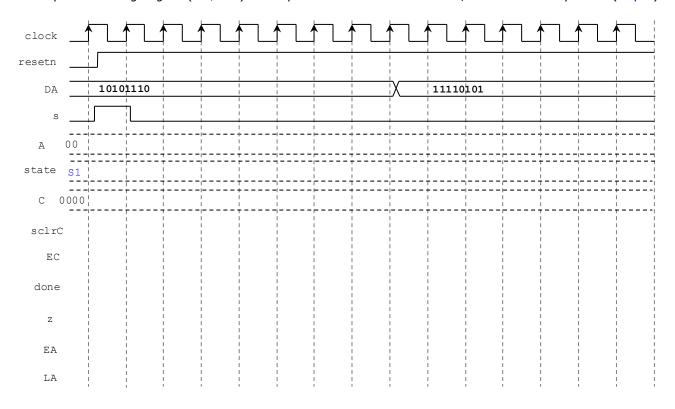

• Complete the timing diagram (n=8, m=4). A is represented in hexadecimal format, while C is in binary format (12 pts.)

2